摘 要:介紹了VHDL語言及其基本特點(diǎn),討論了VHDL語言在EDA中的諸多優(yōu)點(diǎn),并以交通信號燈主控制電路的設(shè)計為例,說明了用VHDL語言設(shè)計數(shù)字電路的方法以及VHDL語言在數(shù)字電路設(shè)計仿真中的重要作用,給出了交通信號燈主控制電路的時序仿真波形。仿真結(jié)果表明VHDL語言應(yīng)用于數(shù)字電路仿真是切實可行的,在跟蹤性和快速性方面達(dá)到了令人滿意的效果。

關(guān)鍵詞:VHDL;仿真;EDA;數(shù)字電路

隨著電子技術(shù)的發(fā)展,數(shù)字系統(tǒng)的設(shè)計正朝高速度、大容量、小體積的方向發(fā)展,傳統(tǒng)的自 底而上的設(shè)計方法已難以適應(yīng)形勢。EDA(Electronic Design Automation)技術(shù) 的應(yīng)運(yùn)而生,使傳統(tǒng)的電子系統(tǒng)設(shè)計發(fā)生了根本的變革。EDA技術(shù)就是依賴功能強(qiáng)大的計算機(jī),在EDA工具軟件平臺上,對以硬件描述語言VHDL(Very High Speed Integrated Circui t Hardware Description Language)為系統(tǒng)邏輯描述手段自頂而下地逐層完成相應(yīng)的描述 、綜合、優(yōu)化、仿真與驗證,直至生成器件。VHDL語言是目前應(yīng)用于數(shù)字系統(tǒng)仿真為實 用的語言之一。

1VHDL特點(diǎn)

VHDL語言早由美國國防部提出。用VHDL語言進(jìn)行數(shù)字邏輯電路和數(shù)字系統(tǒng)的設(shè)計,是電子電路設(shè)計方法上的一次革命性變革。與傳統(tǒng)設(shè)計方法相比,VHDL描述電路行為的算法有很多優(yōu)點(diǎn):

(1) 設(shè)計層次較高、用于較復(fù)雜的計算時,能盡早發(fā)現(xiàn)存在的問題,縮短設(shè)計周期。

(2) 獨(dú)立實現(xiàn),修改方便,系統(tǒng)硬件描述能力強(qiáng)。

(3) 可讀性好,有利于交流,適合于文檔保存。

(4) VHDL語言標(biāo)準(zhǔn)、規(guī)范、移植性強(qiáng)。

(5) VHDL類型眾多而且支持用戶自定義類型,支持自頂而下的設(shè)計方法和多種電路的設(shè)計。

2數(shù)字系統(tǒng)的設(shè)計流程

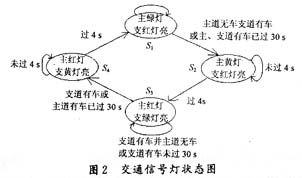

VHDL按要求對系統(tǒng)進(jìn)行描述,然后綜合、仿真、適配,當(dāng)確認(rèn)設(shè)計符合要求時,再將設(shè)計映 射至實際的邏輯器件中,設(shè)計流程如圖1所示。

![]()

VHDL語言已日益成為一種通用的硬件設(shè)計交換媒介,計算機(jī)輔助工程軟件的供應(yīng)商已把VHDL作為其CAD或EDA軟件輸入與輸出的標(biāo)準(zhǔn)。其中ALTERA公司提供了一套十分有特色的綜合工具M(jìn)AX+PLUSⅡ,他提供了全面的邏輯設(shè)計能力,從編輯、綜合、布線到仿真、下載一氣呵成,十分方便。

3設(shè)計實例及仿真結(jié)果

3.1設(shè)計實例

以交通信號燈主控制電路的設(shè)計為例,應(yīng)用MAX+PLUSⅡ軟件平臺,來說明VHDL語言在EDA仿真中的應(yīng)用。設(shè)有一個主干道與支干道的交叉路口,每邊都設(shè)有紅、黃、綠信號燈,設(shè)計一 個控制器優(yōu)先保證主干道的暢通。該設(shè)計實例的基本功能描述為:

(1)平時處于“主干道綠燈,支道紅燈”狀態(tài),只有在支道有車輛要穿行主干道時,才將交通燈切向“主干道紅燈,支道綠燈”。

(2)一旦支道無車輛通過路口,交通燈又回到“主干道綠燈,支道紅燈”的狀態(tài)。

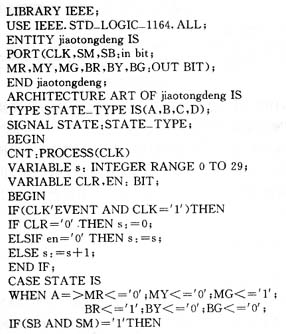

(3)主干道和支干道每次通行的時間不得短于30 s,在兩個狀態(tài)交換過程出現(xiàn) “主黃,支紅”和“主紅,支黃”狀態(tài),持續(xù)時間都是4 s。該功能描述的狀態(tài)圖如圖2所示。

因為主干道和支干道各有3種燈(紅、黃、綠),他們在正常工作時,發(fā)亮的燈只有4種可能:

(1)主綠燈和支紅燈亮——主干道通行。

(2)主黃燈和支紅燈亮——主干道停車。

(3)主紅燈和支綠燈亮——支干道通行。

(4)主紅燈和支黃燈亮——支干道停車。

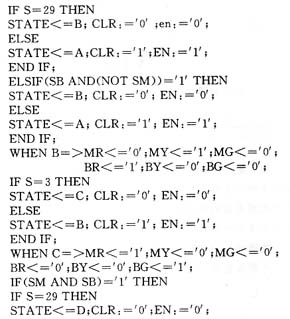

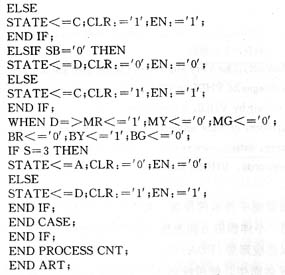

根據(jù)交通燈信號控制的要求,可把他分解為定時器和控制器兩部分。CLK:時鐘脈沖;SM :主干道來車信號;SB:支干道來車信號;MR:主干道紅燈;MY:主干道黃燈;MG:主干道 綠燈;BR:支干道紅燈;BY:支干道黃燈;BG:支干道綠燈。主控制電路設(shè)計程序如下:

3.2仿真結(jié)果分析

利用MAX+PLUSⅡ?qū)τ蒝HDL編寫的主控制電路程序進(jìn)行編譯和仿真,由分析知,主干道和支干道的控制燈正常工作時只有4種狀態(tài),而這4種狀態(tài)完全取決于按鍵SM(主干道來車信號)和SB(支干道來車信號),故本設(shè)計主控制電路的仿真結(jié)果共有4個,由于當(dāng)SM和SB都是 低電平(為0)時,所有的指示燈都為低電平,即都不被點(diǎn)亮,故可分3種情況討論仿真結(jié)果,由于篇幅所限,本文只給出主干道有車、支干道有車時的仿真結(jié)果。

當(dāng)主、支干道都有車時,這種情況相對復(fù)雜,他體現(xiàn)了控制器的精華部分,為了把此時的仿真波形更加具體化,特分3張圖來詳細(xì)說明其工作過程,如圖3所示。

由圖3(a)知,控制器剛開始工作時,主干道綠燈、支干道紅燈被點(diǎn)亮,控制器處于狀態(tài)S1(本設(shè)計輸出延遲0.5 s,符合要求)。由圖3(b)分析知,當(dāng)主、支干道都有車時,狀態(tài)S1保持到第30 s后,開始轉(zhuǎn)向狀態(tài)S2,即主干道由黃燈轉(zhuǎn)為綠燈亮并保持4 s,支干道紅 燈持續(xù)亮并也保持4 s,4 s后,控制器開始向狀態(tài)S3轉(zhuǎn)變,主干道由黃燈亮轉(zhuǎn)為紅燈亮,支干道由 紅燈亮轉(zhuǎn)化為綠燈亮。由圖3(a)和(b)知當(dāng)主支干道都有車時前半階段支干道的紅燈被點(diǎn) 亮的時間等于主干道黃燈和綠燈的時間被點(diǎn)亮的時間(34 s),符合前述的設(shè)計情況。

狀態(tài)S3一直保持了30 s,即在第64 s時發(fā)生了變化,開始向狀態(tài)S4轉(zhuǎn)變,支干道由綠燈亮轉(zhuǎn) 化為黃燈亮,主干道繼續(xù)保持紅燈亮4 s,4 s過后,也就是在第68 s時,控制器又由狀態(tài)S4 轉(zhuǎn)變?yōu)闋顟B(tài)S1,主干道由紅燈亮轉(zhuǎn)化為綠燈亮,支干道由黃燈亮轉(zhuǎn)變?yōu)榧t燈亮,完成了一個 周期的控制工作,由圖3(c)知在一個周期的下半段主干道紅燈亮的時間等于支干道黃燈和綠 燈被點(diǎn)亮的時間之和(34 s),經(jīng)分析知此程序完全實現(xiàn)了前述的控制要求。

4結(jié)語

EDA技術(shù)徹底改變了數(shù)字系統(tǒng)的設(shè)計方法和實現(xiàn)手段,借助于硬件描述語言的國際標(biāo)準(zhǔn)VHDL 和強(qiáng)大的EDA工具,可減少設(shè)計風(fēng)險并縮短周期,隨著VHDL語言使用范圍的日益擴(kuò)大,必將 給硬件設(shè)計領(lǐng)域帶來巨大的改革。

參考文獻(xiàn)

[1]侯伯亨.VHDL硬件描述語言與數(shù)字邏輯電路設(shè)計[M].西安:西安 電子科技大學(xué)出版社,1999.

[2]Xilinx Inc.The Programmable Logic Data Book[Z].Xilinc Inc,USA: 1998.