本文介紹幾種實用的抗干擾措施,在硬件抗干擾方面闡述了供電系統的設計、電路板的合理布局以及輸入干擾的抑制幾個實例。解決單片機應用系統實時性強,干擾因素較多的問題。

單片機應用系統的抗干擾設計是系統設計的重要內容之一,抗干擾性能的好壞將決定系統能否在復雜的電磁環境下穩定可靠地工作,從而決定了系統的實際使用價值。特別是在各種實時控制的遠距離系統中,由于現場環境惡劣,干擾因素較多,系統不可避免地要受到其他電磁設備的干擾,若僅按常規設計就很難保證系統的正常運行。因此,抗干擾問題是設計者必須充分考慮和解決的,下面從硬件方面談談抗干擾設計。

一、供電系統

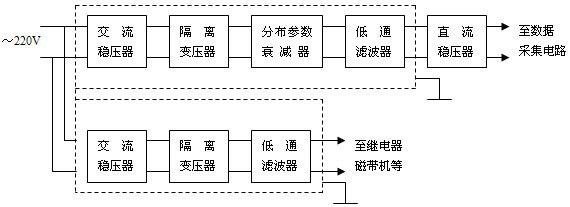

為了防止從電源系統引入干擾,首先采用交流穩壓器保證供電系統的穩定性,防止電源的過壓和欠壓。其次,電源濾波和退耦是抑制電源干擾的主要方式,可將電源變壓器的初級隔離起來,使混入初級的噪聲干擾不致進入次級;使用隔離變壓器濾掉高頻噪聲,低通濾波器濾掉工頻干擾。

當系統中使用繼電器、磁帶等電感設備時,數據采集的供電電路應與繼電器的供電電路分開,以避免在供電線路之間的干擾,即如圖1所示。

對單片機系統的主機部分使用單獨的穩壓電路,必要時輸入、輸出供電分別采用DC-DC模塊,避免各個部分之間的干擾。

圖1 分別供電的系統示意圖

二、非EPROM芯片空間

MCS-51有64K程序系統空間,一般除了EPROM芯片占用的地址外,還剩余大片未編程的EPROM空間。當PC跑飛進入這些空間時,讀入數據為0FFH,對51系列而言,相當于指令MOVR7,A,將修改R7的內容。

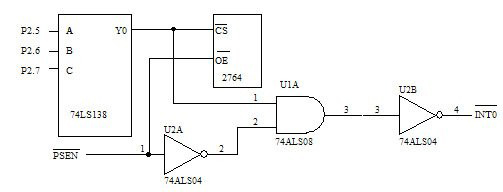

當CPU讀程序存儲器時,會產生一個PSEN的低電平信號,可利用該信號和EPROM的地址譯碼信號產生選通信號,引起一個空閑的中斷,在中斷服務程序中設置軟件陷阱,將跑飛程序拉入正規。圖2是一個實例。

圖2 非EPROM區程序陷阱實例